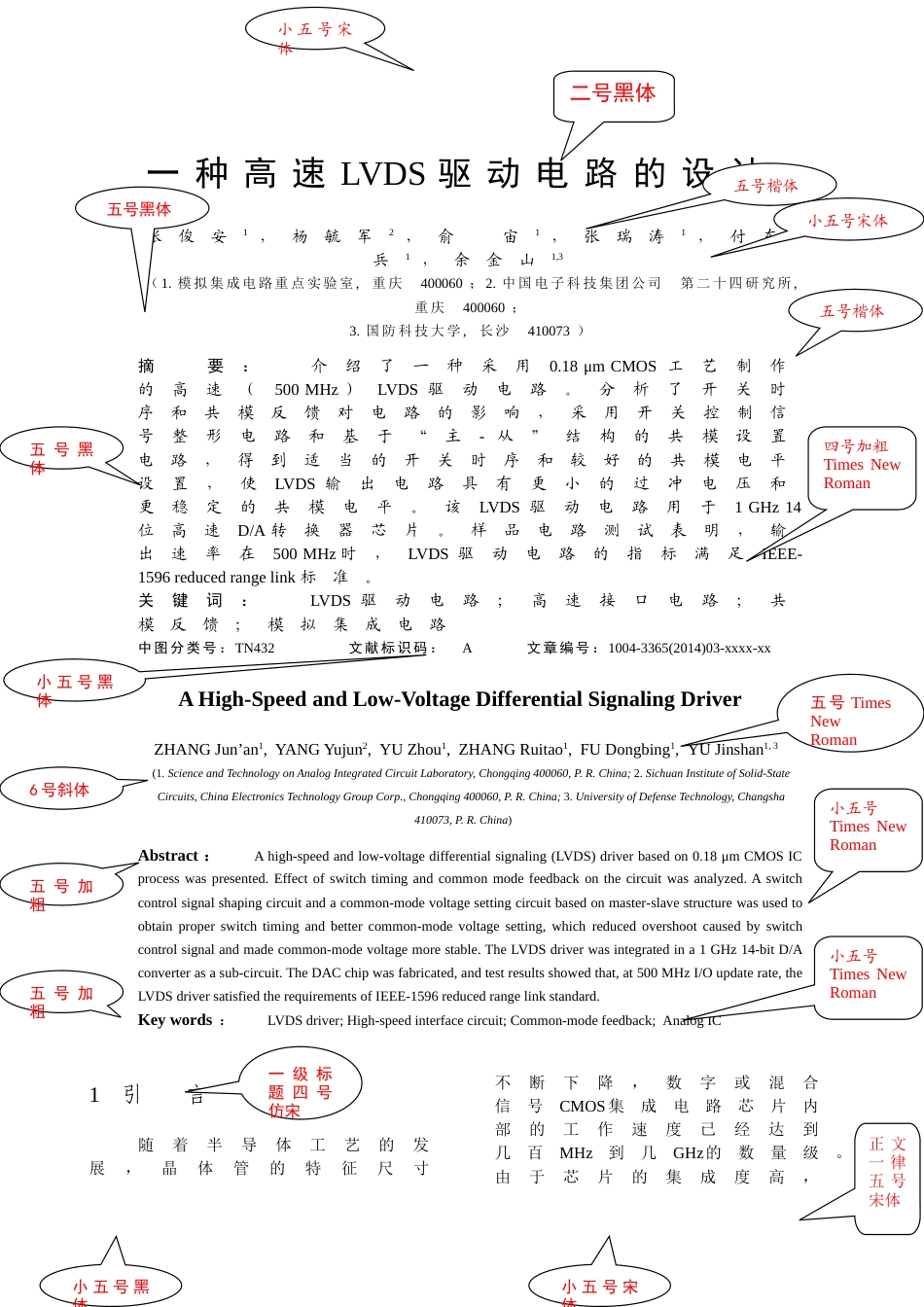

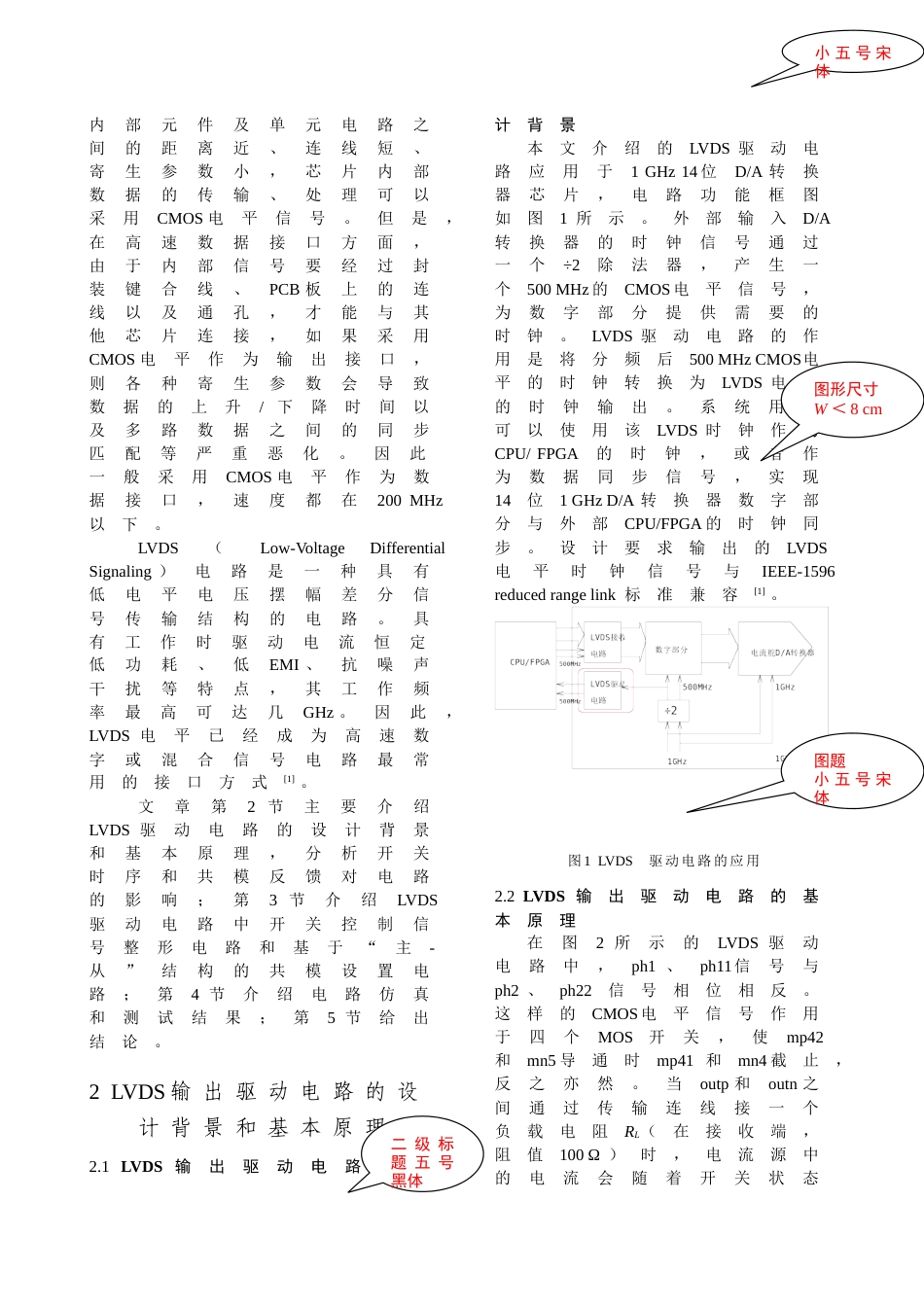

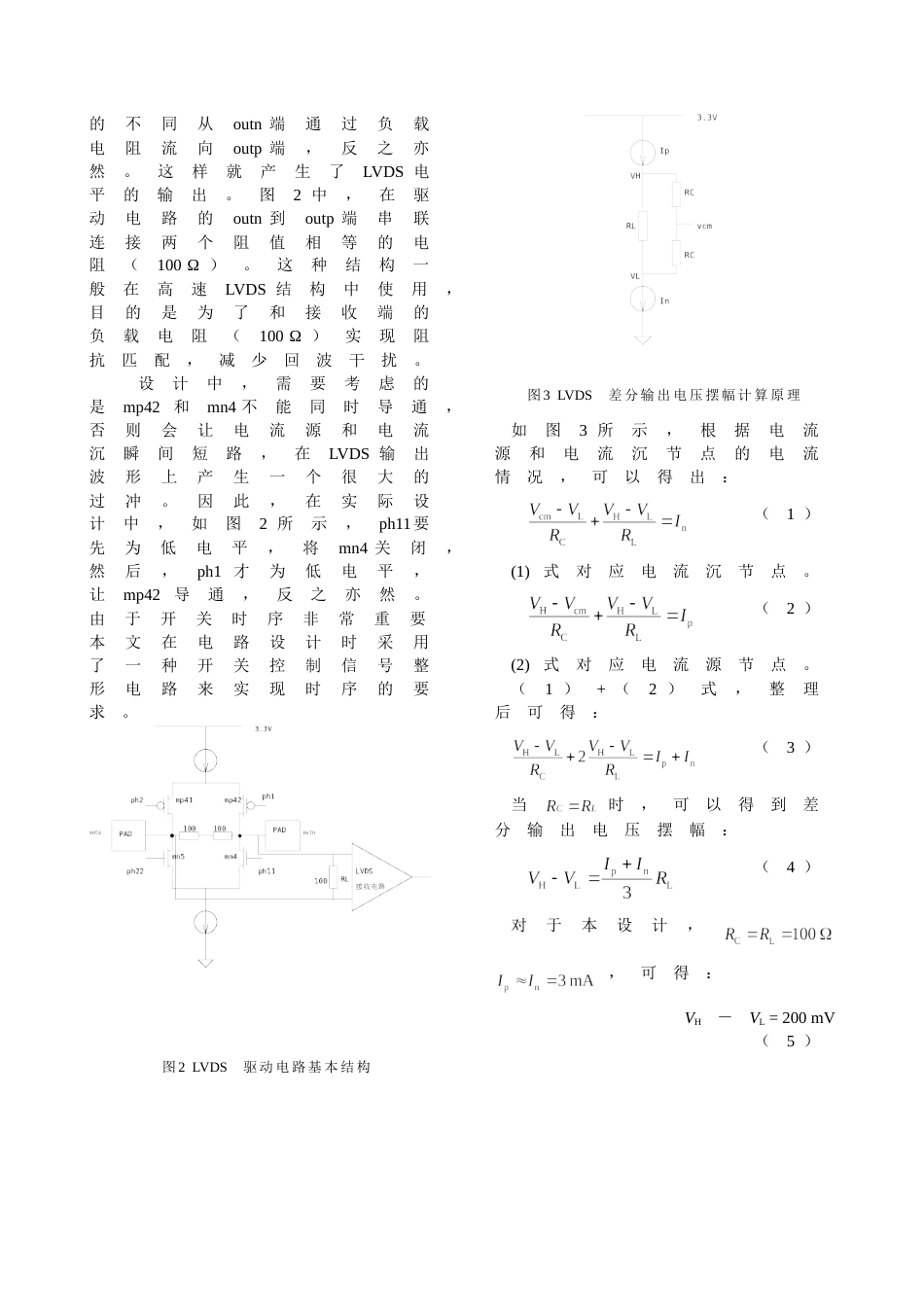

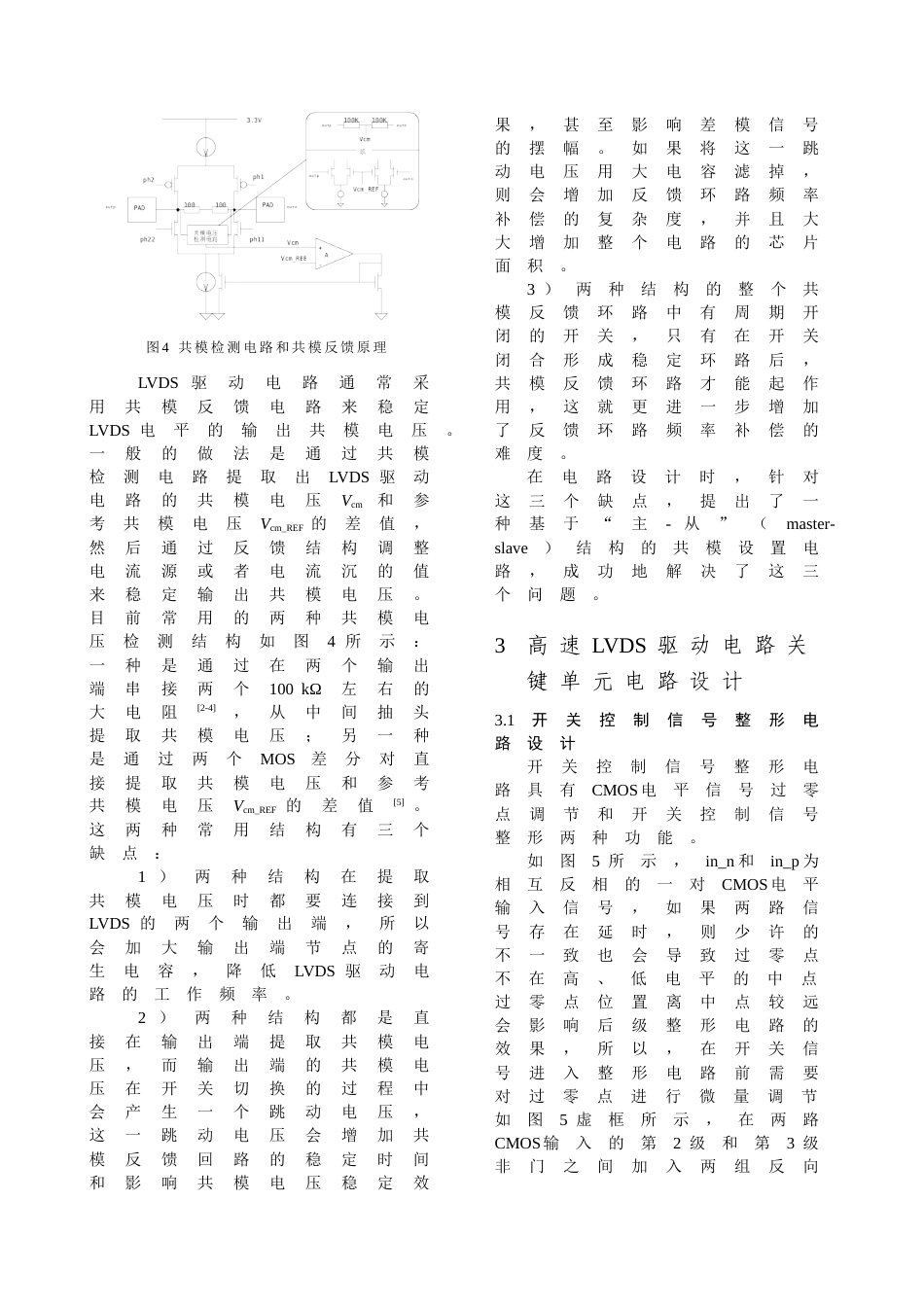

一种高速LVDS驱动电路的设计张俊安1,杨毓军2,俞宙1,张瑞涛1,付东兵1,余金山1,3(1.模拟集成电路重点实验室,重庆400060;2.中国电子科技集团公司第二十四研究所,重庆400060;3.国防科技大学,长沙410073)摘要:介绍了一种采用0.18μmCMOS工艺制作的高速(500MHz)LVDS驱动电路。分析了开关时序和共模反馈对电路的影响,采用开关控制信号整形电路和基于“主-从”结构的共模设置电路,得到适当的开关时序和较好的共模电平设置,使LVDS输出电路具有更小的过冲电压和更稳定的共模电平。该LVDS驱动电路用于1GHz14位高速D/A转换器芯片。样品电路测试表明,输出速率在500MHz时,LVDS驱动电路的指标满足IEEE-1596reducedrangelink标准。关键词:LVDS驱动电路;高速接口电路;共模反馈;模拟集成电路中图分类号:TN432文献标识码:A文章编号:1004-3365(2014)03-xxxx-xxAHigh-SpeedandLow-VoltageDifferentialSignalingDriverZHANGJun’an1,YANGYujun2,YUZhou1,ZHANGRuitao1,FUDongbing1,YUJinshan1,3(1.ScienceandTechnologyonAnalogIntegratedCircuitLaboratory,Chongqing400060,P.R.China;2.SichuanInstituteofSolid-StateCircuits,ChinaElectronicsTechnologyGroupCorp.,Chongqing400060,P.R.China;3.UniversityofDefenseTechnology,Changsha410073,P.R.China)Abstract:Ahigh-speedandlow-voltagedifferentialsignaling(LVDS)driverbasedon0.18μmCMOSICprocesswaspresented.Effectofswitchtimingandcommonmodefeedbackonthecircuitwasanalyzed.Aswitchcontrolsignalshapingcircuitandacommon-modevoltagesettingcircuitbasedonmaster-slavestructurewasusedtoobtainproperswitchtimingandbettercommon-modevoltagesetting,whichreducedovershootcausedbyswitchcontrolsignalandmadecommon-modevoltagemorestable.TheLVDSdriverwasintegratedina1GHz14-bitD/Aconverterasasub-circuit.TheDACchipwasfabricated,andtestresultsshowedthat,at500MHzI/Oupdaterate,theLVDSdriversatisfiedtherequirementsofIEEE-1596reducedrangelinkstandard.Keywords:LVDSdriver;High-speedinterfacecircuit;Common-modefeedback;AnalogIC1引言随着半导体工艺的发展,晶体管的特征尺寸不断下降,数字或混合信号CMOS集成电路芯片内部的工作速度已经达到几百MHz到几GHz的数量级。由于芯片的集成度高,二号黑体五号楷体小五号宋体五号楷体五号黑体五号黑体小五号黑体四号加粗TimesNewRoman五号TimesNewRoman6号斜体五号加粗五号加粗小五号TimesNewRoman小五号TimesNewRoman一级标题四号仿宋正文一律五号宋体小五号黑体小五号宋体小五号宋体内部元件及单元电路之间的距离近、连线短、寄生参数小,芯片内部数据的传输、处理可以采用CMOS电平信号。但是,在高速数据接口方面,由于内部信号要经过封装键合线、PCB板上的连线以及通孔,才能与其他芯片连接,如果采用CMOS电平作为输出接口,则各种寄生参数会导致数据的上升/下降时间以及多路数据之间的同步匹配等严重恶化。因此一般采用CMOS电平作为数据接口,速度都在200MHz以下。LVDS(Low-VoltageDifferentialSignaling)电路是一种具有低电平电压摆幅差分信号传输结构的电路。具有工作时驱动电流恒定低功耗、低EMI、抗噪声干扰等特点,其工作频率最高可达几GHz。因此,LVDS电平已经成为高速数字或混合信号电路最常用的接口方式[1]。文章第2节主要介绍LVDS驱动电路的设计背景和基本原理,分析开关时序和共模反馈对电路的影响;第3节介绍LVDS驱动电路中开关控制信号整形电路和基于“主-从”结构的共模设置电路;第4节介绍电路仿真和测试结果;第5节给出结论。2LVDS输出驱动电路的设计背景和基本原理2.1LVDS输出驱动电路的设计背景本文介绍的LVDS驱动电路应用于1GHz14位D/A转换器芯片,电路功能框图如图1所示。外部输入D/A转换器的时钟信号通过一个÷2除法器,产生一个500MHz的CMOS电平信号,为数字部分提供需要的时钟。LVDS驱动电路的作用是将分频后500MHzCMOS电平的时钟转换为LVDS电平的时钟输出。系统用户可以使用该LVDS时钟作为CPU/FPGA的时钟,或者作为...