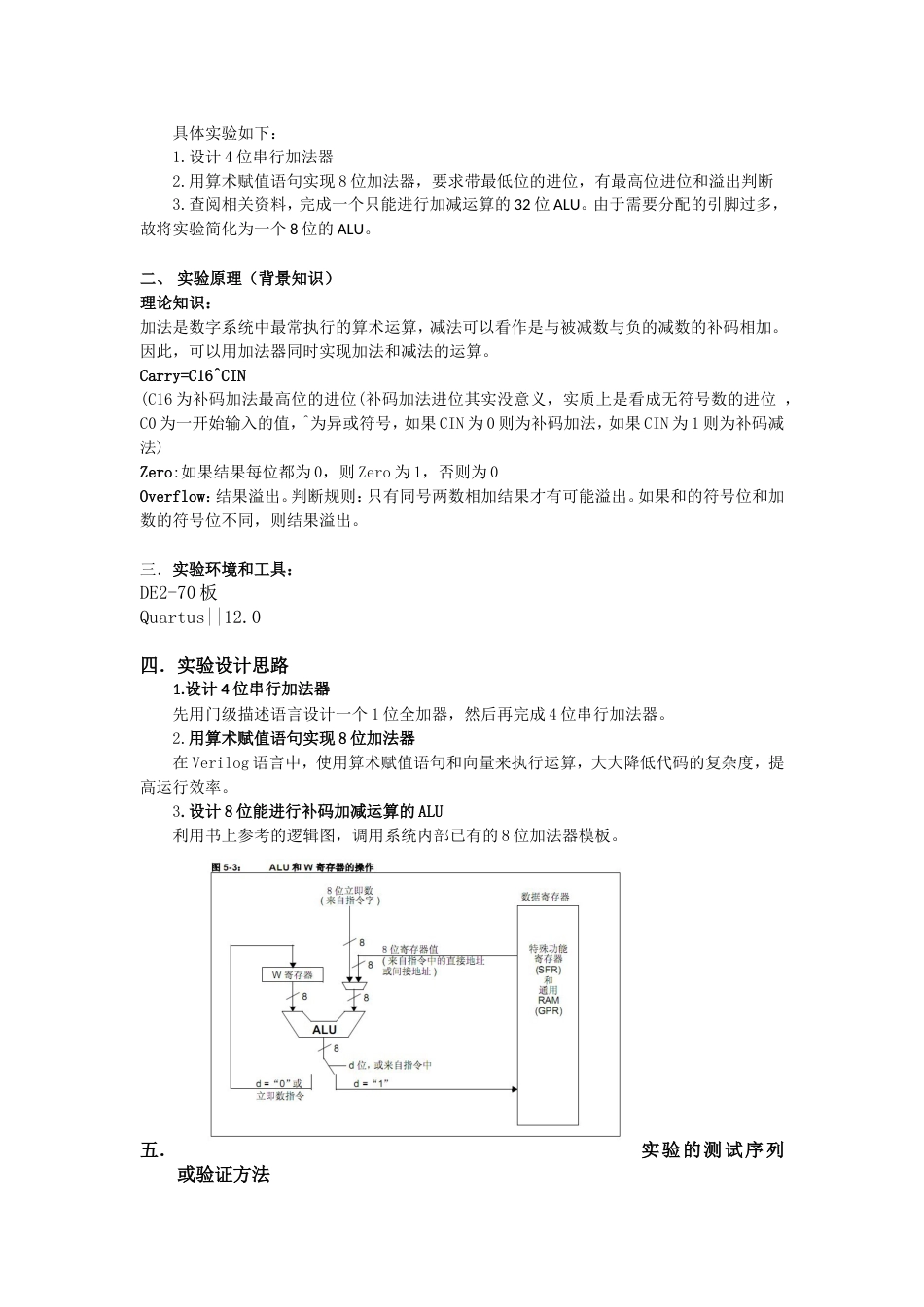

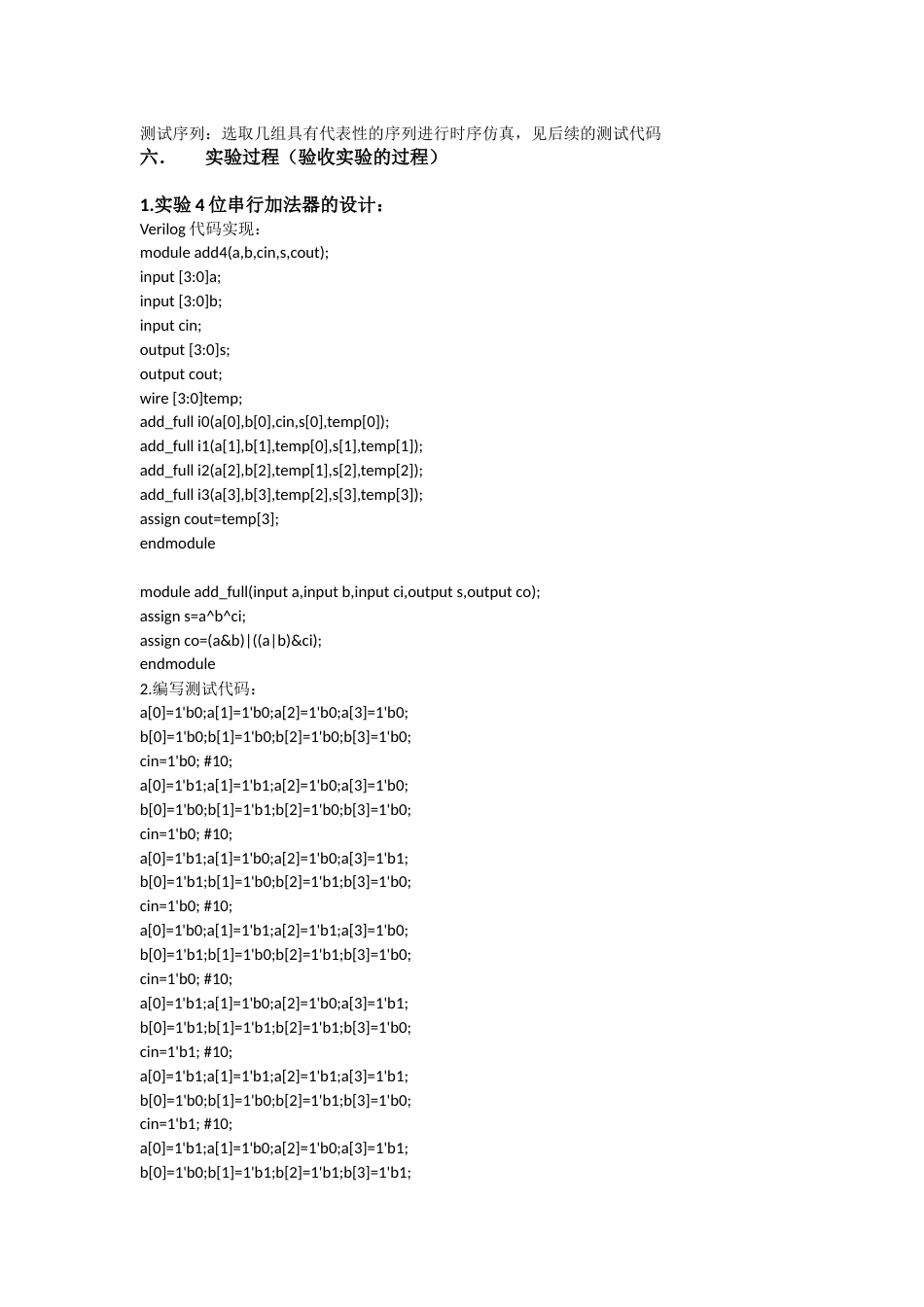

《数字逻辑电路》实验报告课程名称:数字逻辑电路实验实验编号:05实验名称:简单加法器设计报告时间:2013.10.31一、实验目的本实验的目的是复习一位全加器的原理,学习用门级语言、算术赋值语句和利用Altera公司提供的参数化功能模块完成加法器的设计,比较理解各种设计方式的优劣。具体实验如下:1.设计4位串行加法器2.用算术赋值语句实现8位加法器,要求带最低位的进位,有最高位进位和溢出判断3.查阅相关资料,完成一个只能进行加减运算的32位ALU。由于需要分配的引脚过多,故将实验简化为一个8位的ALU。二、实验原理(背景知识)理论知识:加法是数字系统中最常执行的算术运算,减法可以看作是与被减数与负的减数的补码相加。因此,可以用加法器同时实现加法和减法的运算。Carry=C16^CIN(C16为补码加法最高位的进位(补码加法进位其实没意义,实质上是看成无符号数的进位,C0为一开始输入的值,^为异或符号,如果CIN为0则为补码加法,如果CIN为1则为补码减法)Zero:如果结果每位都为0,则Zero为1,否则为0Overflow:结果溢出。判断规则:只有同号两数相加结果才有可能溢出。如果和的符号位和加数的符号位不同,则结果溢出。三.实验环境和工具:DE2-70板Quartus||12.0四.实验设计思路1.设计4位串行加法器先用门级描述语言设计一个1位全加器,然后再完成4位串行加法器。2.用算术赋值语句实现8位加法器在Verilog语言中,使用算术赋值语句和向量来执行运算,大大降低代码的复杂度,提高运行效率。3.设计8位能进行补码加减运算的ALU利用书上参考的逻辑图,调用系统内部已有的8位加法器模板。五.实验的测试序列或验证方法测试序列:选取几组具有代表性的序列进行时序仿真,见后续的测试代码六.实验过程(验收实验的过程)1.实验4位串行加法器的设计:Verilog代码实现:moduleadd4(a,b,cin,s,cout);input[3:0]a;input[3:0]b;inputcin;output[3:0]s;outputcout;wire[3:0]temp;add_fulli0(a[0],b[0],cin,s[0],temp[0]);add_fulli1(a[1],b[1],temp[0],s[1],temp[1]);add_fulli2(a[2],b[2],temp[1],s[2],temp[2]);add_fulli3(a[3],b[3],temp[2],s[3],temp[3]);assigncout=temp[3];endmodulemoduleadd_full(inputa,inputb,inputci,outputs,outputco);assigns=a^b^ci;assignco=(a&b)|((a|b)&ci);endmodule2.编写测试代码:a[0]=1'b0;a[1]=1'b0;a[2]=1'b0;a[3]=1'b0;b[0]=1'b0;b[1]=1'b0;b[2]=1'b0;b[3]=1'b0;cin=1'b0;#10;a[0]=1'b1;a[1]=1'b1;a[2]=1'b0;a[3]=1'b0;b[0]=1'b0;b[1]=1'b1;b[2]=1'b0;b[3]=1'b0;cin=1'b0;#10;a[0]=1'b1;a[1]=1'b0;a[2]=1'b0;a[3]=1'b1;b[0]=1'b1;b[1]=1'b0;b[2]=1'b1;b[3]=1'b0;cin=1'b0;#10;a[0]=1'b0;a[1]=1'b1;a[2]=1'b1;a[3]=1'b0;b[0]=1'b1;b[1]=1'b0;b[2]=1'b1;b[3]=1'b0;cin=1'b0;#10;a[0]=1'b1;a[1]=1'b0;a[2]=1'b0;a[3]=1'b1;b[0]=1'b1;b[1]=1'b1;b[2]=1'b1;b[3]=1'b0;cin=1'b1;#10;a[0]=1'b1;a[1]=1'b1;a[2]=1'b1;a[3]=1'b1;b[0]=1'b0;b[1]=1'b0;b[2]=1'b1;b[3]=1'b0;cin=1'b1;#10;a[0]=1'b1;a[1]=1'b0;a[2]=1'b0;a[3]=1'b1;b[0]=1'b0;b[1]=1'b1;b[2]=1'b1;b[3]=1'b1;cin=1'b1;#10;3.仿真测试结果2.用算术赋值语句实现8位加法器Verilog代码modulewoadd(iSW,X,cin,cout,S,overflow,zero);input[7:0]iSW,X;inputcin;output[7:0]S;outputcout,overflow,zero;wireC;assign{cout,S}=cin+iSW+X;assignC=X[7]^iSW[7]^S[7];assignoverflow=cout^C;assignzero=S[0]|S[1]|S[2]|S[3]|S[4]|S[5]|S[6]|S[7];endmodule测试和仿真结果3.设计8位能进行补码加减运算的ALU实验电路图:实验测试和仿真效果:七.实验结果1.用Verilog代码成功实现了一个4位串行进位的加法器2.用算术赋值语句成功实现了一个8位串行加法器3.设计了一个能进行补码加减运算的8位ALU,根据控制端完成加,减和判断是否为0等运算。八.实验中遇到的问题及解决方案1.开发板的引脚数数目不够32位数运算解决方案:实验中将32位的输入改成了8位输入,成功解决了此项技术瓶颈2.一开始不清楚何谓门级描述语言,后来上网查询资料才知道,就是用Verilog语言中的~异或,&与门,|或门等逻辑描述语句来实现九.实验的启示/意见和建议1.更加熟练学会使用在module中套用另外一个module,从而减少verilog语言的复杂度。2.学会灵活地将问题分化分几个小问题来实现。3.门级描述语言的含义,如上已经介绍。4.模板ALU的输入已经默认为输入补码,在设计好电路之后,我还没有意识到这个问题,以至于验收的时候没有得到预料中的输出结果,在反复调试了开发板之后,终于明白了。即最高位已经默认为符号位5.学会了调用TOOLS中已经存在的ALU模板进行设计更加复杂的电路,从而简化了原来设计的电路图。