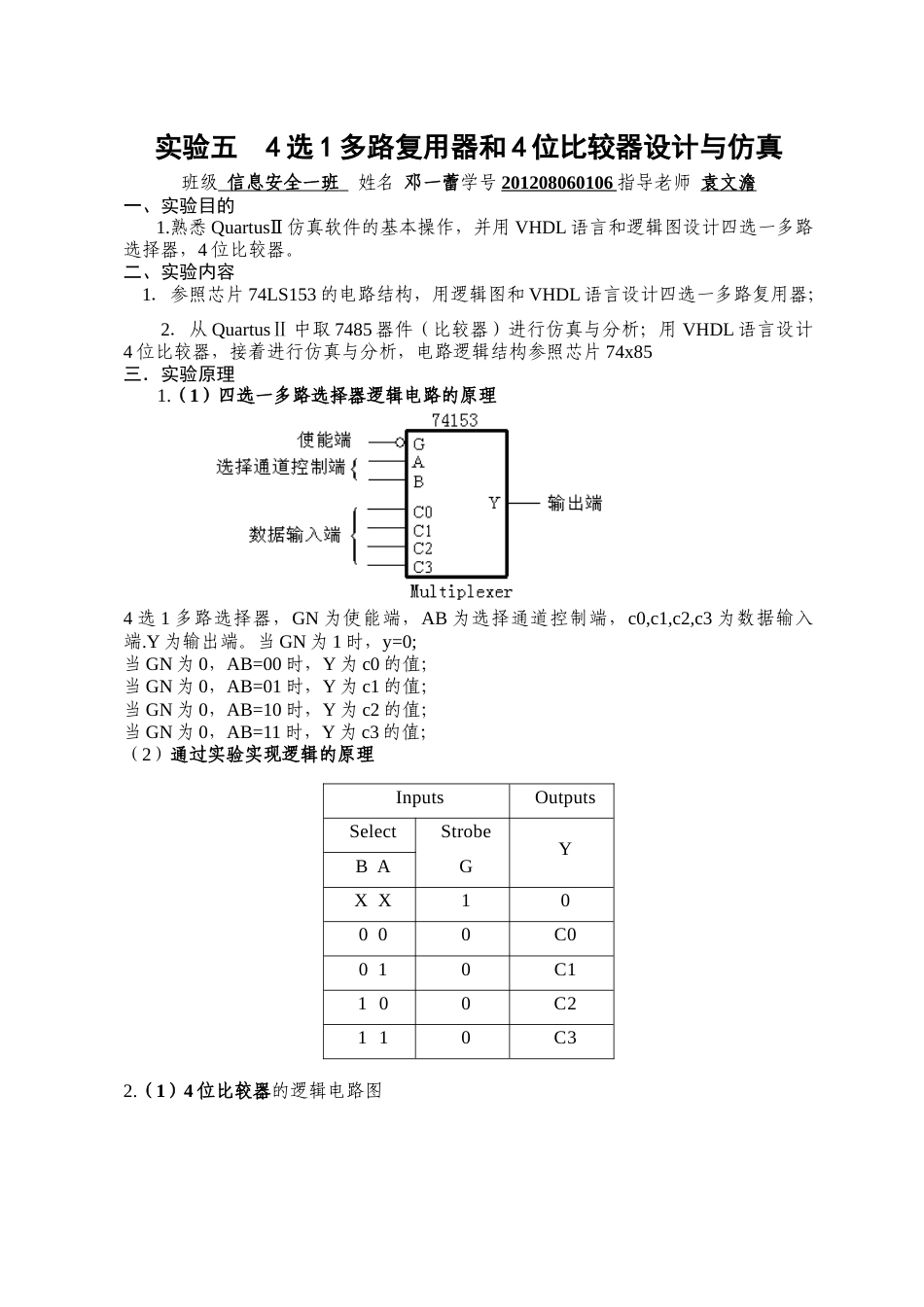

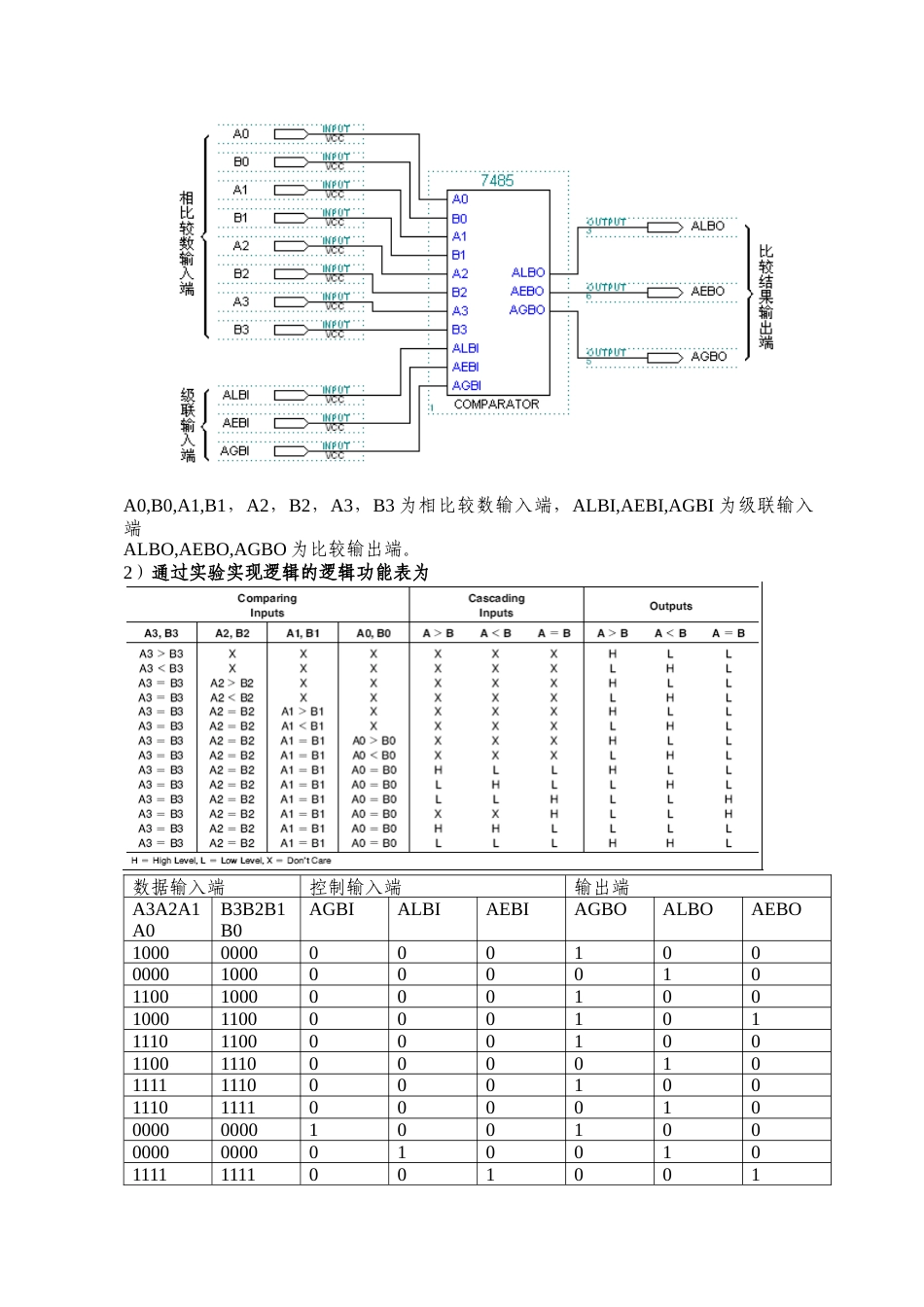

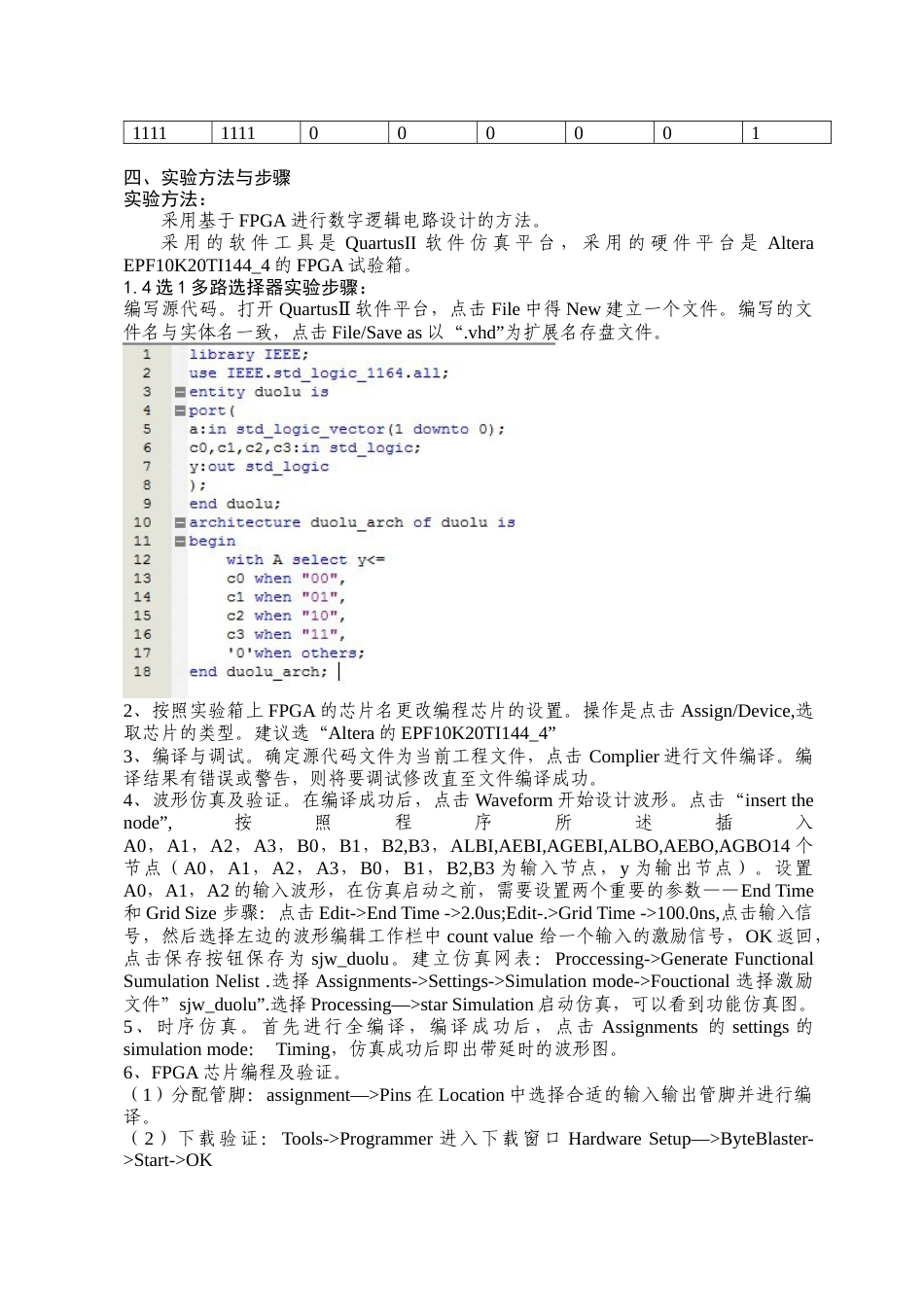

实验五4选1多路复用器和4位比较器设计与仿真班级信息安全一班姓名邓一蕾学号201208060106指导老师袁文澹一、实验目的1.熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言和逻辑图设计四选一多路选择器,4位比较器。二、实验内容1.参照芯片74LS153的电路结构,用逻辑图和VHDL语言设计四选一多路复用器;2.从QuartusⅡ中取7485器件(比较器)进行仿真与分析;用VHDL语言设计4位比较器,接着进行仿真与分析,电路逻辑结构参照芯片74x85三.实验原理1.(1)四选一多路选择器逻辑电路的原理4选1多路选择器,GN为使能端,AB为选择通道控制端,c0,c1,c2,c3为数据输入端.Y为输出端。当GN为1时,y=0;当GN为0,AB=00时,Y为c0的值;当GN为0,AB=01时,Y为c1的值;当GN为0,AB=10时,Y为c2的值;当GN为0,AB=11时,Y为c3的值;(2)通过实验实现逻辑的原理InputsOutputsSelectStrobeGYBAXX10000C0010C1100C2110C32.(1)4位比较器的逻辑电路图A0,B0,A1,B1,A2,B2,A3,B3为相比较数输入端,ALBI,AEBI,AGBI为级联输入端ALBO,AEBO,AGBO为比较输出端。2)通过实验实现逻辑的逻辑功能表为数据输入端控制输入端输出端A3A2A1A0B3B2B1B0AGBIALBIAEBIAGBOALBOAEBO100000000001000000100000001011001000000100100011000001011110110000010011001110000010111111100001001110111100001000000000100100000000000100101111111100100111111111000001四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是AlteraEPF10K20TI144_4的FPGA试验箱。1.4选1多路选择器实验步骤:编写源代码。打开QuartusⅡ软件平台,点击File中得New建立一个文件。编写的文件名与实体名一致,点击File/Saveas以“.vhd”为扩展名存盘文件。2、按照实验箱上FPGA的芯片名更改编程芯片的设置。操作是点击Assign/Device,选取芯片的类型。建议选“Altera的EPF10K20TI144_4”3、编译与调试。确定源代码文件为当前工程文件,点击Complier进行文件编译。编译结果有错误或警告,则将要调试修改直至文件编译成功。4、波形仿真及验证。在编译成功后,点击Waveform开始设计波形。点击“insertthenode”,按照程序所述插入A0,A1,A2,A3,B0,B1,B2,B3,ALBI,AEBI,AGEBI,ALBO,AEBO,AGBO14个节点(A0,A1,A2,A3,B0,B1,B2,B3为输入节点,y为输出节点)。设置A0,A1,A2的输入波形,在仿真启动之前,需要设置两个重要的参数——EndTime和GridSize步骤:点击Edit->EndTime->2.0us;Edit-.>GridTime->100.0ns,点击输入信号,然后选择左边的波形编辑工作栏中countvalue给一个输入的激励信号,OK返回,点击保存按钮保存为sjw_duolu。建立仿真网表:Proccessing->GenerateFunctionalSumulationNelist.选择Assignments->Settings->Simulationmode->Fouctional选择激励文件”sjw_duolu”.选择Processing—>starSimulation启动仿真,可以看到功能仿真图。5、时序仿真。首先进行全编译,编译成功后,点击Assignments的settings的simulationmode:Timing,仿真成功后即出带延时的波形图。6、FPGA芯片编程及验证。(1)分配管脚:assignment—>Pins在Location中选择合适的输入输出管脚并进行编译。(2)下载验证:Tools->Programmer进入下载窗口HardwareSetup—>ByteBlaster->Start->OK(3)初始化电路,根据设置好的管脚资源擦做实验电路板,完成数据测试。五、实验结果与分析1、编译过程a)编译过程、调试结果b)结果分析及结论编译成功,可继续下一步骤。2、功能仿真a)功能仿真过程及仿真结果选择processing---->GenerateFunctionalSimulationNetlist产生功能仿真网格---->Assigentnents--->Settings----->Functional---->Processing--->StartSimulation,启动功能仿真b)结果分析及结论GN为0,AB为00时,y=c0;GN为0,AB为01时,y=c1;GN为0,AB为10时,y=c2;GN为0,AB为11时,y=c3;3.时序仿真a)时序仿真过程及仿真结果b)结果分析及结论仿真结果与逻辑存在偏差,因为时序仿真存在延迟现象,是正常现象。Programming芯片编程a)芯片编程过程管脚分配:b)编程芯片FPGA验证结果c)结果分...