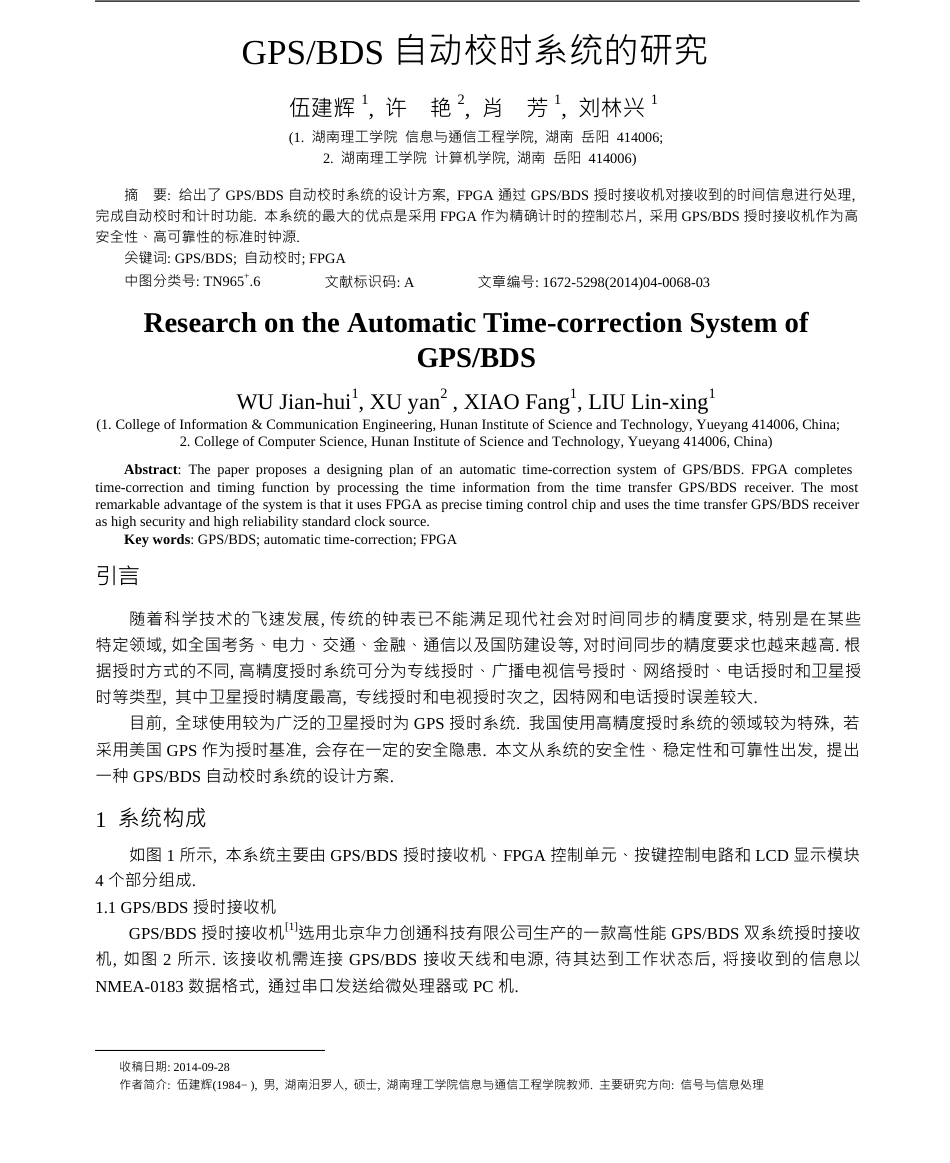

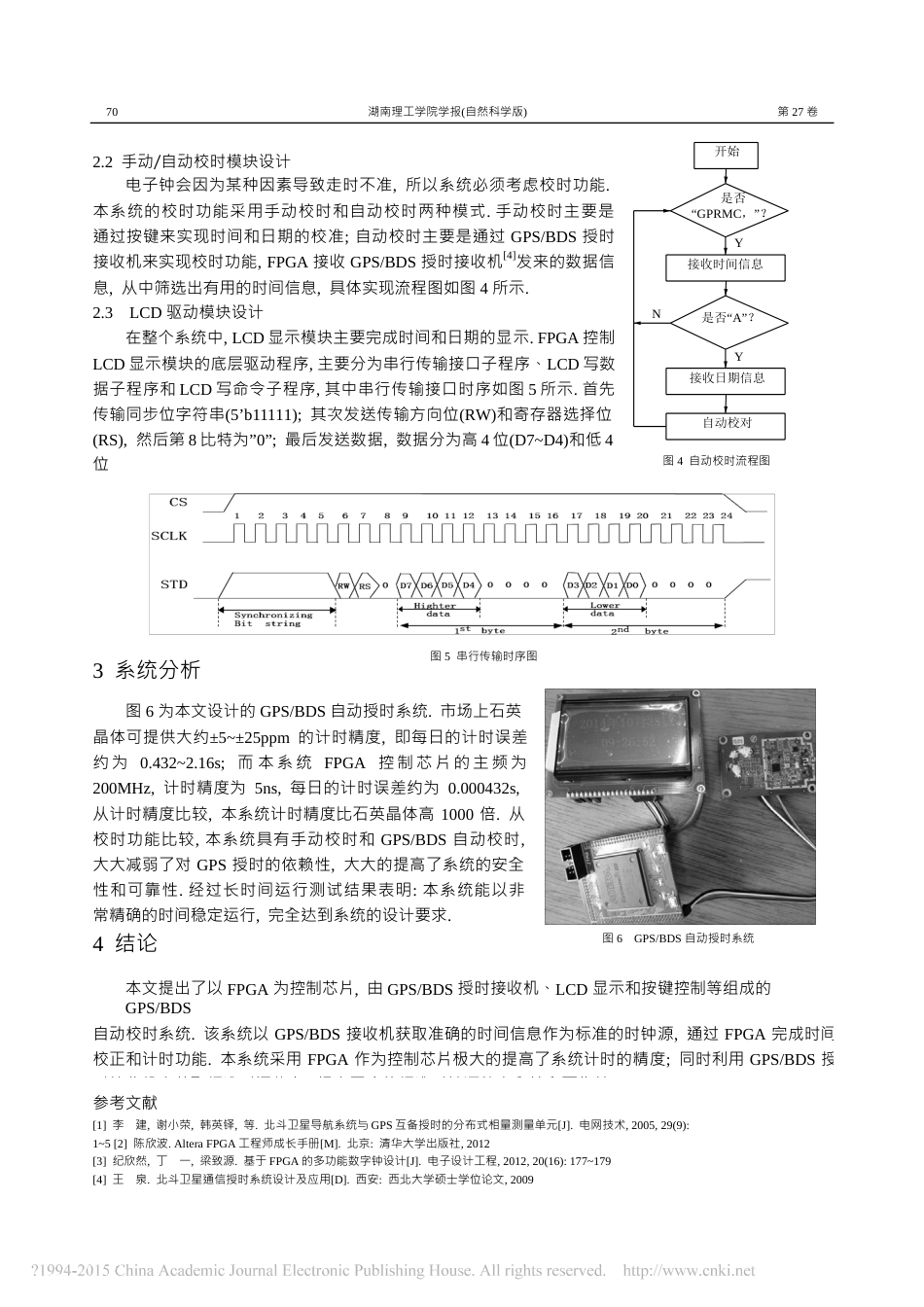

GPS/BDS自动校时系统的研究伍建辉1,许艳2,肖芳1,刘林兴1(1.湖南理工学院信息与通信工程学院,湖南岳阳414006;2.湖南理工学院计算机学院,湖南岳阳414006)摘要:给出了GPS/BDS自动校时系统的设计方案,FPGA通过GPS/BDS授时接收机对接收到的时间信息进行处理,完成自动校时和计时功能.本系统的最大的优点是采用FPGA作为精确计时的控制芯片,采用GPS/BDS授时接收机作为高安全性、高可靠性的标准时钟源.关键词:GPS/BDS;自动校时;FPGA中图分类号:TN965+.6文献标识码:A文章编号:1672-5298(2014)04-0068-03ResearchontheAutomaticTime-correctionSystemofGPS/BDSWUJian-hui1,XUyan2,XIAOFang1,LIULin-xing1(1.CollegeofInformation&CommunicationEngineering,HunanInstituteofScienceandTechnology,Yueyang414006,China;2.CollegeofComputerScience,HunanInstituteofScienceandTechnology,Yueyang414006,China)Abstract:Thepaperproposesadesigningplanofanautomatictime-correctionsystemofGPS/BDS.FPGAcompletestime-correctionandtimingfunctionbyprocessingthetimeinformationfromthetimetransferGPS/BDSreceiver.ThemostremarkableadvantageofthesystemisthatitusesFPGAasprecisetimingcontrolchipandusesthetimetransferGPS/BDSreceiverashighsecurityandhighreliabilitystandardclocksource.Keywords:GPS/BDS;automatictime-correction;FPGA引言随着科学技术的飞速发展,传统的钟表已不能满足现代社会对时间同步的精度要求,特别是在某些特定领域,如全国考务、电力、交通、金融、通信以及国防建设等,对时间同步的精度要求也越来越高.根据授时方式的不同,高精度授时系统可分为专线授时、广播电视信号授时、网络授时、电话授时和卫星授时等类型,其中卫星授时精度最高,专线授时和电视授时次之,因特网和电话授时误差较大.目前,全球使用较为广泛的卫星授时为GPS授时系统.我国使用高精度授时系统的领域较为特殊,若采用美国GPS作为授时基准,会存在一定的安全隐患.本文从系统的安全性、稳定性和可靠性出发,提出一种GPS/BDS自动校时系统的设计方案.1系统构成如图1所示,本系统主要由GPS/BDS授时接收机、FPGA控制单元、按键控制电路和LCD显示模块4个部分组成.1.1GPS/BDS授时接收机GPS/BDS授时接收机[1]选用北京华力创通科技有限公司生产的一款高性能GPS/BDS双系统授时接收机,如图2所示.该接收机需连接GPS/BDS接收天线和电源,待其达到工作状态后,将接收到的信息以NMEA-0183数据格式,通过串口发送给微处理器或PC机.收稿日期:2014-09-28作者简介:伍建辉(1984−),男,湖南汨罗人,硕士,湖南理工学院信息与通信工程学院教师.主要研究方向:信号与信息处理第4期伍建辉,等:GPS/BDS自动校时系统的研究69FPGA控制单元天线图2GPS/BDS授时接收机图1GPS/BDS自动校时系统框图1.2FPGA控制单元FPGA控制单元[2]采用的是Altera公司的CycloneⅢ系列产品EP3C16Q240C8,具有15408个逻辑单元、504KB的RAM资源、56个18×18乘法器、4个PLL,可用I/O数达136个.FPGA通过芯片的第100、101脚与GPS/BDS授时接收机通讯;通过第81、82、83、84、85脚控制LCD显示模块;通过第86、87、93、94脚对按键进行检测;通过第112、111、110、108脚对LED指示灯进行控制.1.3LCD显示模块LCD显示模块选用的是C系列128×64中文液晶显示模块,可以显示字母、符号、中文字型和图形.设置LCD显示模块PSB引脚为低电平,FPGA采用串行方式,通过CS、SCLK、STD引脚对显示模块进行显示控制.2系统软件设计本系统以FPGA[3]为硬件平台,采用VerilogHDL语言,在QuartusⅡ开发软件中设计GPS/BDS自动校时系统,具有计时、手动校时、自动校时和液晶显示功能.2.1计时模块设计计时模块分为时、分、秒计时和年、月、日计时,具体说明如下:(1)以系统时钟作为主频,产生1路秒脉冲;(2)以秒脉冲作为时、分、秒计时的计数时钟信号,若秒计数加至60瞬间,分计数加1,同时秒计数清零;若分计数加至60瞬间,时计数加1,分计数清零;若时计数加至24瞬间,产生1路日脉冲,时计数清零;(3)以日脉冲作为年、月、日计时的计数时钟信号,通过系统辨认本月的总天数(28天、29天、30天、31天四种情况),待日计数等于本...